- سه شنبه ۱۷ خرداد ۱۴۰۱

اصول مدارهای مجتمع دیجیتال برنامهپذیر

اصول مدارهای مجتمع دیجیتال برنامهپذیر

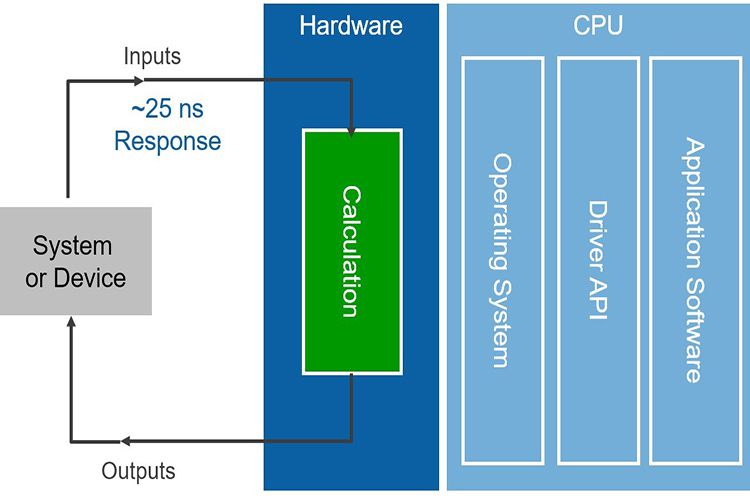

«مدارهای مجتمع دیجیتال برنامهپذیر» یا FPGA (Field-programmable gate arrays) که به آنها «آرایههای دروازه برنامهپذیر در محل» یا «آی.سیهای دیجیتال برنامهپذیر» نیز میگویند، مدارهای مجتمع (integrated circuits) یا آی.سیهایی قابل برنامهریزی مجدد هستند که حاوی آرایهای از بلوکهای منطقی قابل برنامهریزی هستند. دلیل بهکارگیری تراشههای FPGA انعطافپذیری، سرعت، قابل اطمینان بودن و قابلیت موازیسازی آنهاست.

FPGAها برخلاف پردازندهها واقعاً ماهیتی موازی دارند، بنابراین عملیات پردازشی مختلف در رقابت بر سر منابع یکسان قرار نمیگیرند. هر کار پردازشی در یک بخش خاص از تراشه انجام میشود و بهطور مستقل و بدون هیچ گونه تأثیری از سوی سایر بلوکهای منطقی عمل میکند. در نتیجه وقتی پردازشهای بیشتری را دستور دهید، عملکرد یک قسمت از برنامه تحت تأثیر افزایش پردازشها قرار نمیگیرد.

یکی از مزایای FPGA نسبت به سیستمهای مبتنی بر پردازنده این است که منطق برنامه در مدارهای سختافزاری جای گرفته است نه در سیستم عامل، درایوها یا نرمافزارهای کاربردی.(دپارتمان برق و الکترونیک)

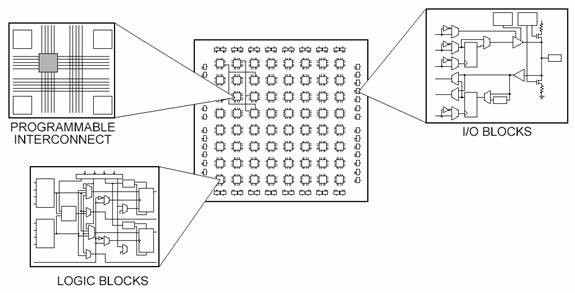

معرفی بخشهای FPGA

هر تراشه FPGA از تعدادی محدود از منابع از پیش تعریفشده ساخته شده است که دارای اتصالات قابل برنامهریزی هستند و میتوان از آنها برای پیادهسازی مدار دیجیتال قابل تنظیم مجدد و بلوکهای ورودی و خروجی استفاده کرد که دسترسی مدار به دنیای خارج را فراهم میکنند.

منابع سخت افزاری در FPGA ها شامل موارد زیر است:

- I/O Blocks

- Logic Blocks

- Multipliers

- Routing Matrix

- Memory

- Clock Blocks

I/O Block ها، مدارات پشت هر کدام از پینهای FPGA هستند که قابلیت برنامهریزی به صورت in، out و ... را دارند. علاوه بر این میتوانیم نوع استاندارد برای هر کدام از پایهها را تعیین کنیم. Logic Block ها از مالتی پلکسر، فلیپ فلاپ و LUT تشکیل شدهاند. وجود LUT امکان طراحی مدارات سنکرون را به ما میدهد. Multiplier (ضربکننده) ها که در پردازش سیگنال بسیار استفاده میشوند، توان مصرفی کمتری دارند و نسبت به LUTها دارای سرعت بالاتری هستند. Routing Matrix شامل سیمها و اتصالات قابل برنامهریزی برای اتصال LUTها است. Memory، RAM های بلوکی به صورت از پیش ساخته در FPGAها وجود دارند و معمولا برای ذخیرهسازی اطلاعات (به جای LUTها) استفاده میشوند. Clock Block ها دارای اهمیت بالایی هستند، چون کلاک مسئله مهمی در پیادهسازی مدارات ترتیبی سنکرون است و معمولا از DCM برای ایجاد کلاکی با فرکانس دلخواه استفاده میشود.

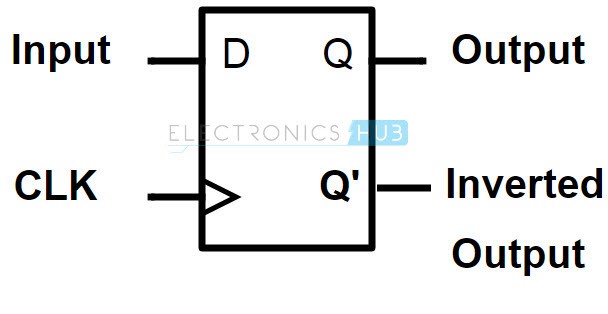

فلیپفلاپ (Flip-Flops)

فلیپفلاپها و لچها (latches) بلوکهای ساختمانی اساسی سیستمهای الکترونیک دیجیتال هستند که در رایانهها، ارتباطات و بسیاری از انواع دیگر سیستمها مورد استفاده هستند. فلیپفلاپ یک مدار الکترونیکی با دو حالت پایدار است که برای ذخیره دادههای دوتایی مورد استفاده قرار میگیرد. دادههای ذخیرهشده را میتوان با اعمال ورودیهای مختلف تغییر داد.

از فلیپفلاپ برای همگامسازی منطقی و ذخیره حالتهای منطقی بین چرخههای ساعت در مدار FPGA استفاده میشود. در هر لبه ساعت، یک فلیپفلاپ مقدار یک یا صفر (درست یا غلط) را در ورودی دارد و آن مقدار را تا لبه ساعت بعدی ثابت نگه میدارد.

بیشتر منطق یک بلوک منطقی قابل تنظیم با استفاده از مقادیر بسیار کمی از RAM به شکل LUT پیادهسازی میشود. بهراحتی میتوان دید که تعداد گیتهای سیستم در یک FPGA به تعداد گیتهای NAND و گیتهای NOR در یک تراشه خاص اشاره دارد. اما در واقعیت تمام منطق ترکیبی (ANDها، ORها، NANDها، XORها و غیره) در واقع بهعنوان جداول ارزش در حافظه جداول جستجو پیادهسازی میشوند. یک جدول ارزش فهرستی از پیش تعریف شده از خروجیها برای هر ترکیبی از ورودیهاست.

همچنین جدول درستی (LUT) برای دو ورودی در عملیات AND بولی بهصورت زیر است:

|

خروجی |

ورودی دو |

ورودی یک |

|

صفر |

صفر |

صفر |

|

صفر |

یک |

صفر |

|

صفر |

صفر |

یک |

|

یک |

یک |

یک |

ضربکنندهها و بلوکهای DSP48

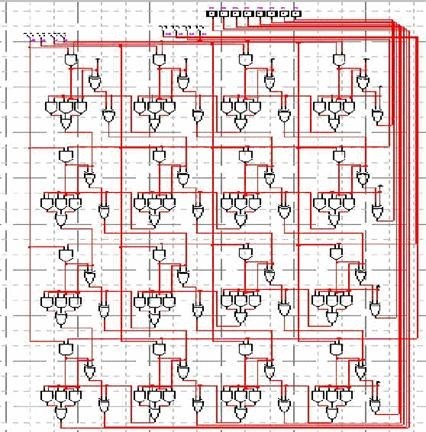

کار بهظاهر ساده ضرب دو عدد با هم میتواند برای مدارهای دیجیتال کاری بهشدت پیچیده و نیازمند منابع بسیار باشد. شکل زیر ترسیم شماتیک راه تأمین چارچوبهای مرجع برای پیادهسازی ضرب ۴بیتی در ۴بیتی با استفاده از منطق ترکیبی است.

حال تصور کنید که دو عدد ۳۲بیتی را بخواهید در هم ضرب کنید که در نهایت بیش از ۲۰۰۰ عملیات برای این ضرب لازم است. به همین دلیل FPGAها مدارهای ضربکننده از پیش ساختهشده دارند تا در استفاده از جداول درستی و فلیپفلاپها در برنامههای ریاضی و پردازش سیگنال صرفهجویی کنند.

بسیاری از الگوریتمهای پردازش سیگنال کار نگه داشتن مجموع اعداد در حال ضرب شدن را انجام میدهند و در نتیجه FPGAهایی که کارایی بالاتری دارند، مانند Xilinx Virtex-5 FPGA دارای مدارهای انباشته ضربکننده از پیش ساختهشده هستند. این بلوکهای پردازشی از پیش ساختهشده را بلوکهای DSP48 مینامند که یک ضربکننده ۲۵ در ۱۸بیتی را با مدار جمعکننده ادغام میکند.

بلوک RAM

منابع حافظه یکی دیگر از مشخصات کلیدی هستند که هنگام انتخاب FPGAها باید به آنها توجه کنید. رم تعریف شده توسط کاربر که در سرتاسر تراشه FPGA تعبیه شده است، برای ذخیره مجموعه دادهها یا انتقال مقادیر بین کارهای موازی مفید است.

بسته به اینکه FPGA از چه خانوادهای است، میتوانید رم داخلی را در بلوکهای ۱۶یا ۳۶بیتی پیکربندی کنید. همچنین میتوانید مجموعه دادهها را با استفاده از فلیپفلاپ به صورت آرایه پیادهسازی کنید.

با این حال، آرایههای بزرگ برای منابع منطقی FPGA گران هستند. یک آرایه با ۱۰۰ قسمت از اعداد ۳۲بیتی بیش از ۳۰درصد فلیپفلاپ یک FPGA Virtex-II هزار یا یک درصد از بلوک رم داخلی را مصرف میکند.

الگوریتمهای پردازش سیگنال دیجیتال اغلب لازم است کل یک بلوک داده یا همه ضرایب یک معادله پیچیده را بررسی کنند و بدون حافظه داخلی، بسیاری از توابع پردازش در منطق قابل تنظیم یک تراشه FPGA جای نمیگیرند.

امکان اجرای موازی (concurrent) کدها در FPGAها به قطعات مستقل منطقی سختافزار اجازه میدهد با کلاکهای مختلف کار کنند. انتقال داده بین مراکز منطقی که با سرعتهای مختلف کار میکنند دشوار است و حافظه داخلی اغلب برای انجام این انتقال مشغول میشود و این کار را به کمک ای.سیهای بافر و ذخیره داده (FIFO) انجام میدهد.

طراحی FPGA در یک سیستم

FPGAها مزایای بسیاری دارند، مانند سرعت، قابلیت اطمینان و انعطافپذیری، اما ملاحظاتی نیز در مورد آنها وجود دارد.

در طول دهه گذشته نوعی معماری ترکیبی که گاه به آن معماری ناهمگن نیز میگویند به وجود آمده است که در آن یک ریزپردازنده را با یک FPGA جفت میکنند که به یک پورت ورودی / خروجی متصل است. در FPGAهای جدید اغلب گیتهای منطقی را با پردازندهها در یک تراشه واحد که به آن System on Chip (SoC) میگویند ترکیب میکنند تا عملکرد محاسباتی افزایش یابد. در این روش از مزایای هر دو بخش استفاده میشود.

ابزارهای طراحی FPGA

حال که با بلوکهای سازنده یک تراشه FPGA آشنا شدید، شاید بپرسید که چگونه همه این میلیونها مؤلفه را برای ایجاد منطق اجرایی مورد نیاز پیکربندی میکنند؟

پاسخ این است که وظایف محاسباتی دیجیتال را در نرمافزار و با استفاده از ابزارهای توسعه تعریف میکنند و سپس آنها را در یک فایل پیکربندی یا بیتاستریم (bitstream) جمع میکنند که حاوی اطلاعاتی در مورد نحوه اتصال اجزا به یکدیگر است.

چالشی که در گذشته در مورد فناوری FPGA وجود داشت این بود که ابزارهای طراحی سطح پایین FPGAها تنها قابل استفاده توسط مهندسانی بودند که درک عمیقی از طراحی سختافزارهای دیجیتال داشتند. اما با ظهور ابزرارهای طراحی سطح بالا یا high-level synthesis (HLS) مانند LabVIEW قوانین برنامهنویسی FPGA تغییر کرد و فناوریهای جدید پدید آمد که نمودارهای بلوکهای گرافیکی را به مدارهای سختافزاری تبدیل میکنند.

ابزارهای سنتی طراحی FPGA

طی بیست سال اول توسعه FPGA، زبانهای توصیف سختافزار یا HDLها مانند VHDL و Verilog به زبانهای اصلی برای طراحی الگوریتمهای در حال اجرا بر روی تراشه FPGA تبدیل شده بودند. این زبانهای سطح پایین برخی از مزایای زبانهای متنی دیگر را داشتند، اگر این نکته را درک میکردید که شما در یک FPGA در حال طراحی یک مدار هستید.

سینتکس ترکیبی حاصل نیاز به سیگنالهایی داشت که از درگاههای ورودی / خروجی خارجی به سیگنالهای داخلی متصل شده و در نهایت به توابعی وصل شود که الگوریتمها را در خود جای میدهند. این توابع بهصورت متوالی اجرا میشوند و میتوانند به توابع دیگر در FPGA ارجاع دهند.

با این حال ماهیت موازی واقعی انجام کار در یک FPGA را بهسختی میتوان بهصورت یک جریان خط به خط متوالی مجسم کرد. زبانهای توصیف سختافزار برخی از ویژگیهای دیگر زبانهای متنی را منعکس میکنند، اما تفاوت عمدهای دارند زیرا مبتنی بر یک مدل جریان داده هستند که در آن ورودی و خروجی از طریق سیگنالها به مجموعهای از بلوکهای تابع متصل میشود.

سپس برای تست منطقی که برنامهنویس FPGA تعیین کرده است، اغلب تست هایی در HDL نوشته میشوند تا اجرای طراحی FPGA از طریق تعیین ورودیها و تأیید خروجیها آزمایش شود. این تستها از طریق قسمت test bench و کد FPGA در یک محیط شبیهسازی شده، اجرا میشوند که رفتار زمانبندی سختافزاری تراشه FPGA را مدلسازی میکند و همه سیگنالهای ورودی و خروجی را به طراح نشان میدهد تا اعتبار آنها را بسنجد. فرایند ساخت test bench و اجرای این شبیهسازی اغلب به زمان بیشتری نسبت به ساختن خود طرح اصلی زبان توصیف سختافزار FPGA نیاز دارد.

وقتی طرح FPGA با استفاده از زبان توصیف سختافزار تهیه و تأیید شد، باید آن را در یک ابزار کامپایل قرار دهید تا منطق مبتنی بر متن را تهیه کند و طی چندین مرحله پیچیده، HDL را در یک فایل پیکربندی یا بیتاستریم حاوی اطلاعات ترکیب کند.

این اطلاعات نشان میدهند که اجزا چگونه باید به هم متصل شوند. اغلب از شما خواسته میشود که به عنوان بخشی از یک فرایند دستی چندمرحلهای، نقشه نام سیگنالها را در پینهای روی تراشه FPGA مورد استفاده خود مشخص کنید.

ابزارهای طراحی FPGA سطح بالا

ظهور ابزارهای گرافیکی طراحی سطح بالا یا HLS مانند LabVIEW برخی از موانع اصلی فرایند سنتی طراحی HDL را برطرف کرده است. محیط برنامهنویسی LabVIEW بهطور ویژه برای برنامهنویسی FPGA مناسب است زیرا بهوضوح موازیسازی و جریان دادهها را نشان میدهد.

بنابراین کاربرانی که در فرایند طراحی سنتی FPGA تجربه دارند و همچنین آنهایی که تجربه ندارند میتوانند از فناوری FPGA بهره ببرند. علاوه بر این، برای اینکه مالکیت معنوی قبلی از بین نرود، میتوانید از LabVIEW برای ادغام VHDL موجود در طرحهای جدید FPGA که در LabVIEW تهیه میکنید استفاده کنید.

از آنجایی که LabVIEW FPGA با سختافزار یکپارچگی بالایی دارد، نیازی به بازنویسی کد در VHDL به منظور رفع محدودیتهای زمان یا منبع نیست و این مشکل در بسیاری از کدهای HLS وجود دارد.

سپس برای شبیهسازی و تأیید رفتار منطقی FPGA میتوانید در LabVIEW ویژگیها را مستقیماً در محیط توسعه انتخاب کنید. همچنین میتوانید بدون داشتن دانش زبان HDL سطح پایین، test bench را برای اعمال طراحی منطقی خود تهیه کنید.

به علاوه انعطافپذیری محیط LabVIEW به کاربران متخصصتر امکان میدهد، زمانبندی و منطق طراحی خود را در شبیهسازهای دقیق مانند Xilinx ISim مدلسازی کنند.

ابزارهای کامپایل LabVIEW FPGA فرایند کامپایل را بهصورت خودکار انجام میدهند. بنابراین میتوانید این فرایند را با کلیک یک دکمه آغاز کنید و با تکمیل فرایند کامپایل، گزارشها و خطاهای احتمالی را دریافت کنید.

اگر خطاهای زمانبندی حاصل طراحی FPGA باشند، LabVIEW مسیرهای مهم را بهصورت گرافیکی برجسته میکند تا فرایند رفع اشکال سریعتر انجام شود.

جمعبندی

مجتمع فنی تهران : به کارگیری فناوری FPGA رو به افزایش است زیرا ابزارهای سطح بالا مانند LabVIEW باعث شدهاند FPGA دسترسپذیرتر شود. با این حال مهم است که ساختار FPGA را بشناسید و درک کنید که وقتی بلوکهای دیاگرام برای اجرا در سیلیکون کامپایل میشوند دقیقاً چه اتفاقی میافتد.

مقایسه و انتخاب سختافزارها بر اساس فلیپفلاپها، LUTها، ضربکنندهها و بلوکهای RAM بهترین شیوه برای انتخاب تراشه FPGA مناسب برای برنامه شماست. درک شیوه استفاده از منابع در طول توسعه بسیار مفید است، بهویژه هنگام بهینهسازی اندازه و سرعت.

جملات کلیدی

· مقایسه و انتخاب سختافزارها بر اساس فلیپفلاپها، LUTها، ضربکنندهها و بلوکهای RAM بهترین شیوه برای انتخاب تراشه FPGA مناسب برای برنامه شماست.

· درک شیوه استفاده از منابع در طول توسعه بسیار مفید است، بهویژه هنگام بهینهسازی اندازه و سرعت.

· مهم است که ساختار FPGA را بشناسید و درک کنید که وقتی بلوکهای دیاگرام برای اجرا در سیلیکون کامپایل میشوند دقیقاً چه اتفاقی میافتد.

· به کارگیری فناوری FPGA رو به افزایش است زیرا ابزارهای سطح بالا مانند LabVIEW باعث شدهاند که FPGA دسترسپذیرتر شود.

منبع: NI.com

مترجم: بهناز دهکردی